2011.10.5

## MEMS-CMOS Integration and Beyond

Hiroyuki Fujita, Agnes-Tixier Mita, Hiroshi Toshiyoshi Center for International Research on Micronano Mechatronics IIS, The University of Tokyo

2011.10.5

## Content

- MEMS trend toward MEMS-CMOS integration

- Examples of MEMS-CMOS integration

- Beyond MEMS-CMOS integration

U-Tokyo

UC Berkeley

**IEMN/CNRS**

Northeastern Univ.

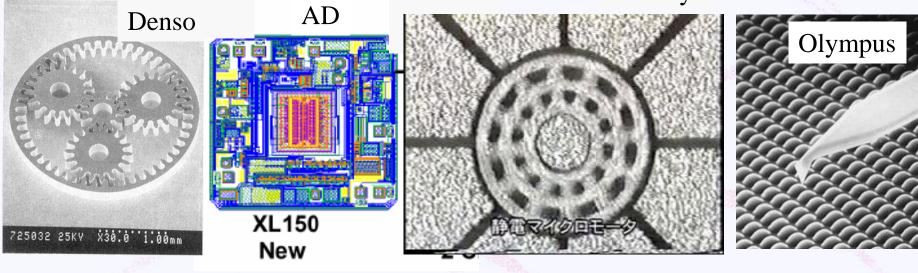

## MEMS Development in Last Decade

Almost all the important processes and devices in micro-scale already existed 10 years ago, e.g. DRIE, bonding, microactuators, etc.

- Technological sophistication,

- Application diversity increase

- Performance improvement.

- Commercial products have flourished.

# Now MEMS is everywhere around you, and even more in the future.

- In your car

- In your camera

- In your smart phone

- In your TV game controller

- In your video projector

- In your printer

- In your computer

- In your (?) robot

Honda Asimo

Nitendo Wii<sup>TM</sup> controller

Digital Light Processing<sup>™</sup> Texas Instrument

## What comes next?

Almost all the important processes and devices in micro-scale already existed 10 years ago, e.g. DRIE, bonding, comb-drive, SDA, etc.

- Technological sophistigation,

- Application diversity increase

- Performance improvement.

- Commercial products have flourished.

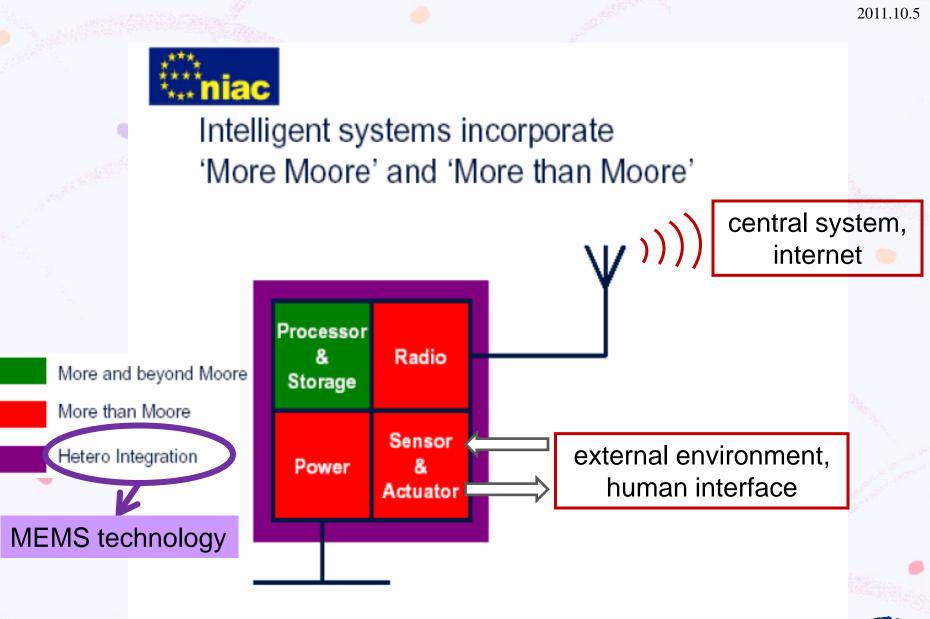

In order to widen the application fields, heterogeneous integration of various functionalities becomes important. (More than Moore approach)

More than Moore, 2005/09/16

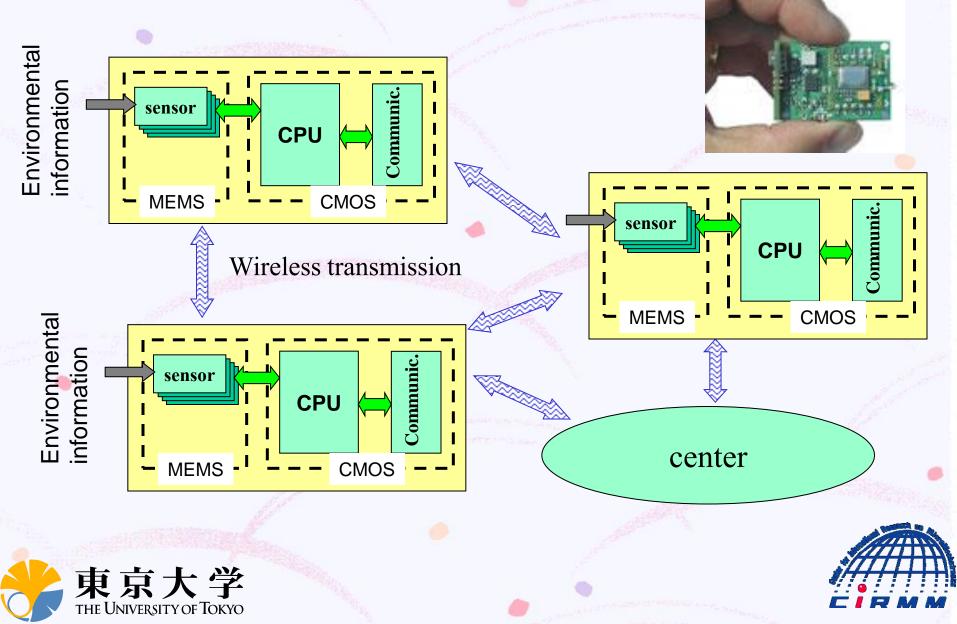

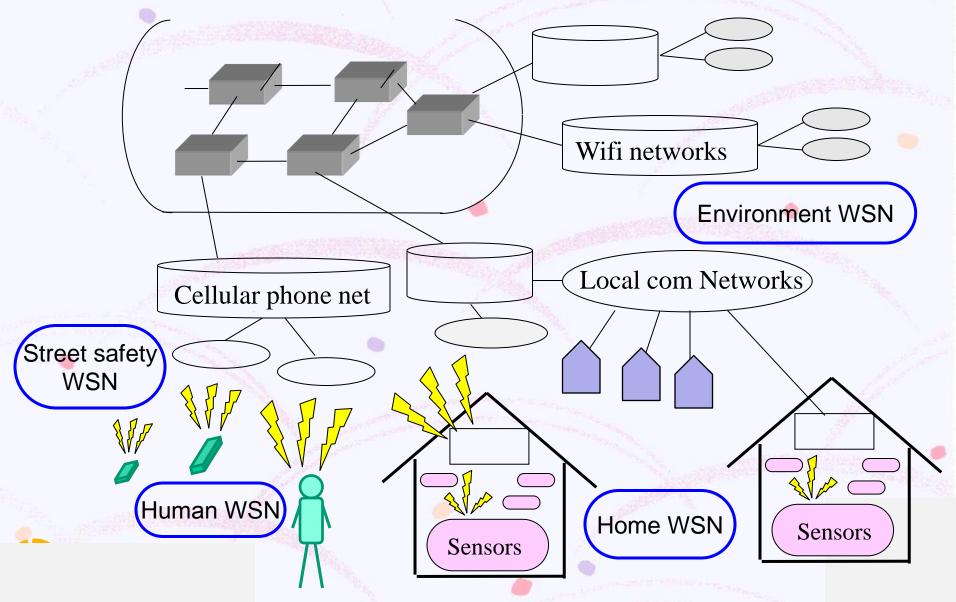

## Micro wireless sensor network

## MEMS wireless senor net(WSN) in communication hierarchy

2011.10.5

2011.10.5

## Content

- MEMS trend toward MEMS-CMOS integration

- Examples of MEMS-CMOS integration

- Beyond MEMS-CMOS integration

## MEMS-CMOS integration methods

- **Hybrid integration**, especially stack integration using TSV

- Monolithic integration by customized fully mixed process

- Monolithic integration by MEMS processing first followed by CMOS process

- Monolithic integration by CMOS processing first followed by MEMS process

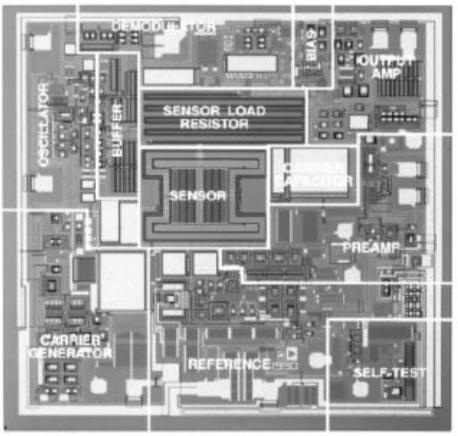

# CMOS-MEMS by surface micromachining ADXL-50 Chip Diagram

Analog Devices' ADXL-50, the industry's first surface micromachined accelerometer, includes signal conditioning on chip.

- Fully mixed fabrication process.

- Poly-Si structure + SiO<sub>2</sub> sacrificial layer.

- Protection of circuits while releasing process is important.

## **MEMS-CMOS** integration methods

- Hybrid integration, especially stack integration using TSV

- Monolithic integration by customized fully mixed process

- Monolithic integration by MEMS processing first followed by CMOS process

- Monolithic integration by CMOS processing first followed by MEMS process

Non-Volatile memory enables rapid configuration of the SiT8002 family to instantly match the form, fit, and function of 100's of fixed frequency oscillators. In addition, the memory never wears out and requires no additional CMOS mask layers, keeping costs low.

SiTime MEMS resonator

300 µm

MEMS-first approach for CMOS circuit integration

Non-Volatile Memory Oscillator 20 µm Drive Encapsulation Layers **Output Buffer** CMOS PLL Fractional-N PLL is used to provide any frequency while consuming 50% less power as compared to traditional Clock IC PLL's.

http://www.sitime.jp/

**Si** Time<sup>®</sup>

The integrated oscillator provides better immunity to ESD as compared to many quartz crystal input pins. In addition, the differential low-noise Boser Oscillator provides excellent immunity to electrical interference as compared to single-ended quartz devices.

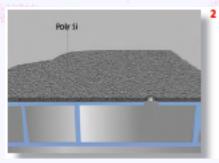

### SiTime MEMS resonator MEMS-first approach for CMOS circuit integration

DRIE of SOI defining resonator (0.4um wide, 10um deep). Trenches filled by SiO2 Thin epi-poly growth. Contacts and etch holes formation.

After sacrificial etching of SiO2, thick epi-poly growth.

Surface polishing and cleaning for next CMOS process. Contact isolation by DRIE Single crystal Si encapsulation layer allows CMOS integration

2011.10.5

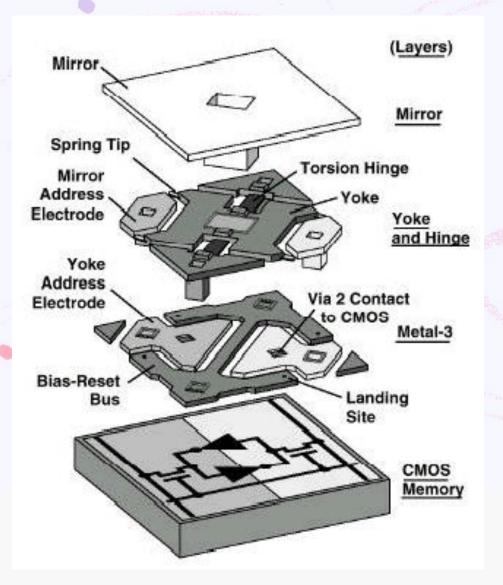

## **MEMS-CMOS** integration methods

- Hybrid integration, especially stack integration using TSV

- Monolithic integration by customized fully mixed process

- Monolithic integration by MEMS processing first followed by CMOS process

- Monolithic integration by CMOS processing first followed by MEMS process

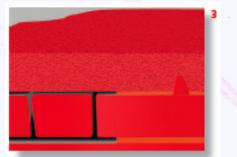

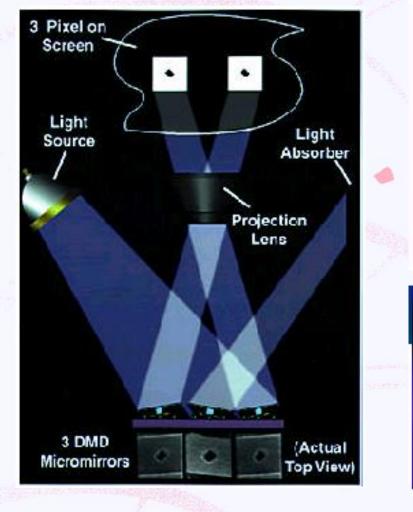

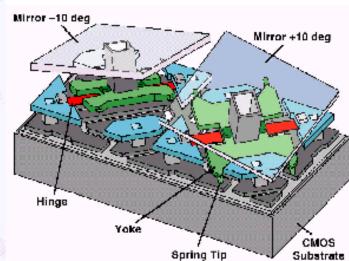

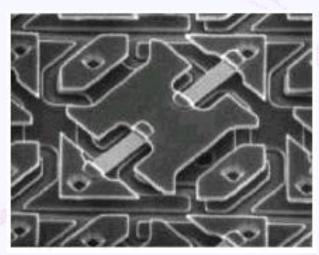

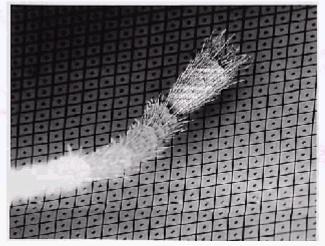

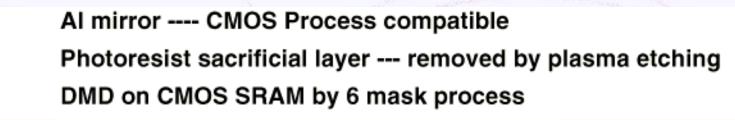

#### **DIGITAL MIRROR DISPLAY (1)** P.F. Van Kessel et al., T.I., Proc. IEEE, Vol. 86, p 1687, 1998

2011.10.5

#### **DIGITAL MIRROR DISPLAY (video)** P.F. Van Kessel et al., T.I., Proc. IEEE, Vol. 86, p 1687, 1998

#### **DIGITAL MIRROR DISPLAY (2)** P.F. Van Kessel et al., T.I., Proc. IEEE, Vol. 86, p 1687, 1998

### **DIGITAL MIRROR DISPLAY (3)** P.F. Van Kessel et al., T.I., Proc. IEEE, Vol. 86, p 1687, 1998

011.10.5

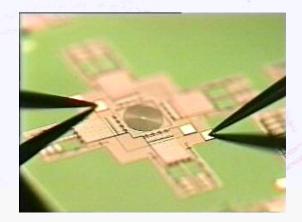

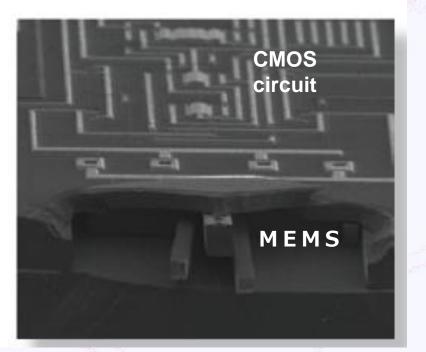

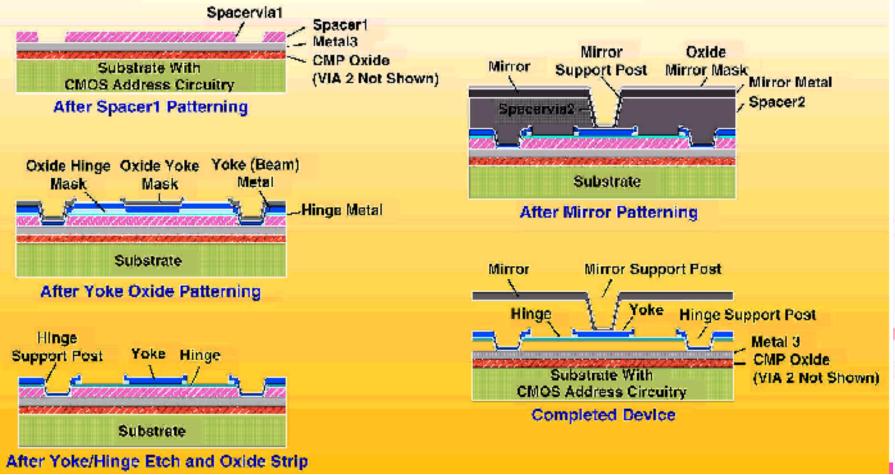

### Post-CMOS metal structure

(a) Cross-section of the nickel MEMS-transistor integration process.(b) Die photo of a fully monolithic micromechanical resonator oscillator using this process. (c) Oscilloscope waveform.

Clark T.-C. Nguyen, UC Berkeley

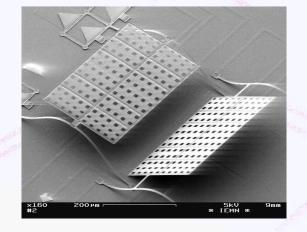

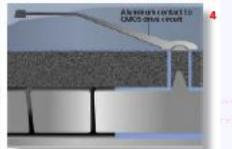

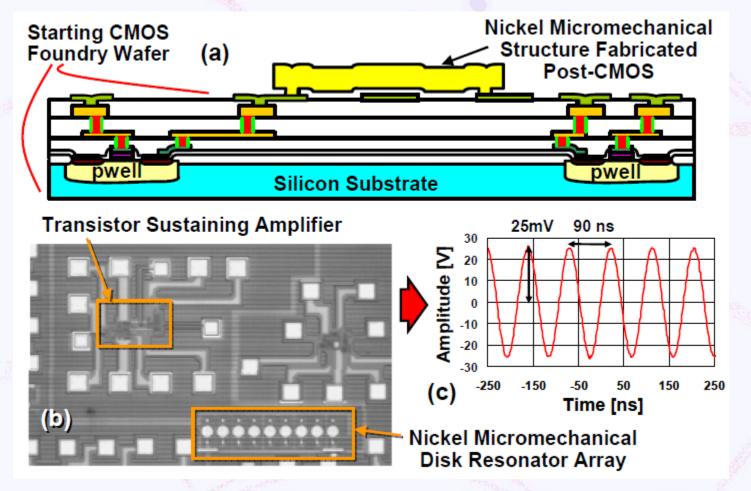

### Post-CMOS MEMS by Deep-RIE

Some space (7 mm x 6 mm) in 40V high-voltage chip is left for post processing of MEMS. MEMS devices are made in 8um-thick active layer of SOI substrate by deep RIE. Handling layer of 625um in thickness can also be structured by RIE. Each of four CMOS segments includes a 16-bit demultiplexer, a 12-bit DA converter, four operational amplifier with sample & holder.

Source: Toshiyoshi Lab. IIS, University of Tokyo

2011.10.5

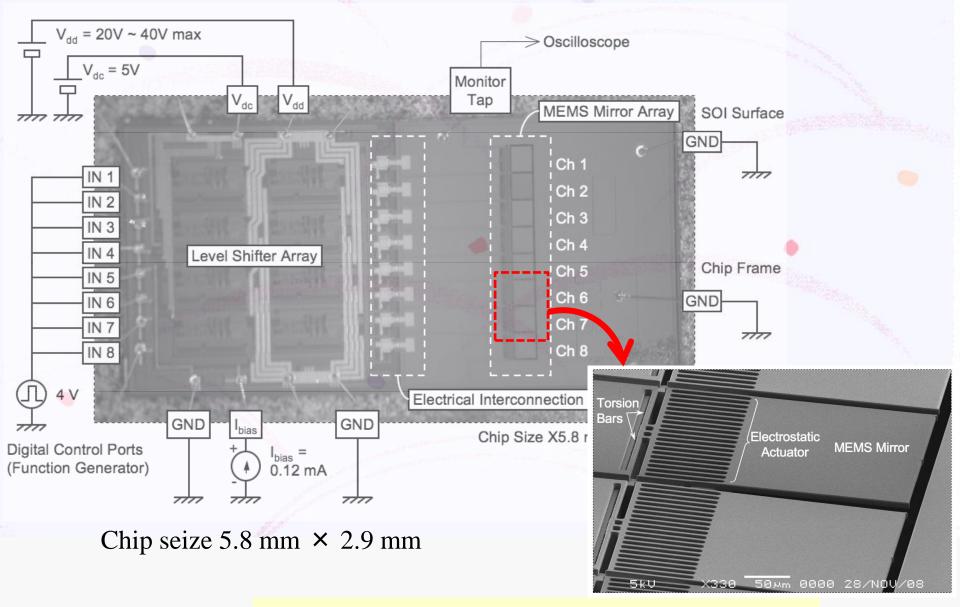

#### A MEMS Digital Mirror Array Integrated with High-voltage Level-shifter

S. Maruyama, K. Takahashi, H. Fujita and H. Toshiyoshi Institute of Industrial Science, The University of Tokyo, Tokyo, Japan

Transducers'09, Denver, CO, USA, June 21-25, p. 2314

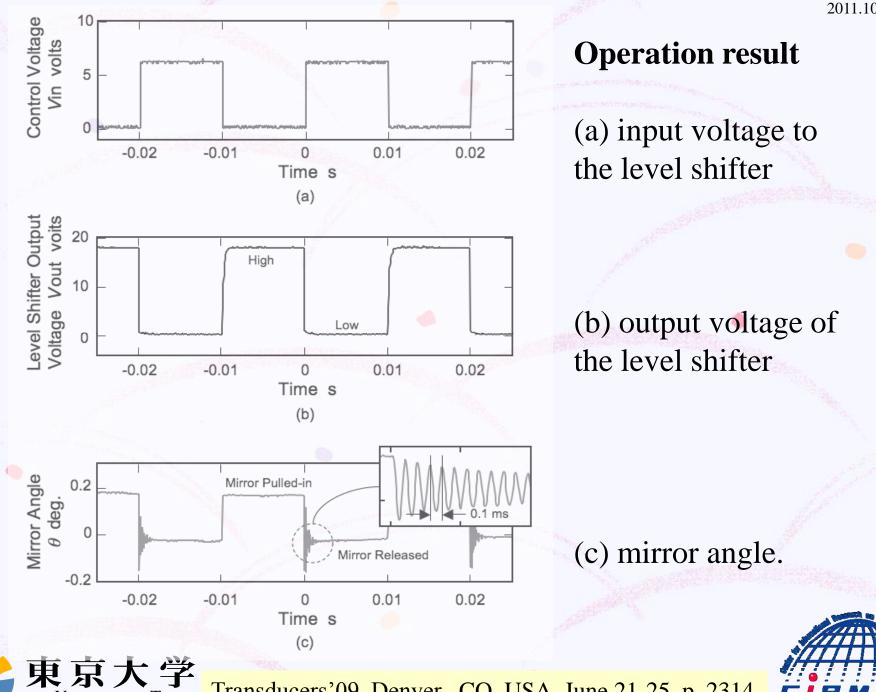

## **CMOS-MEMS** mirror array

Transducers'09, Denver, CO, USA, June 21-25, p. 2314

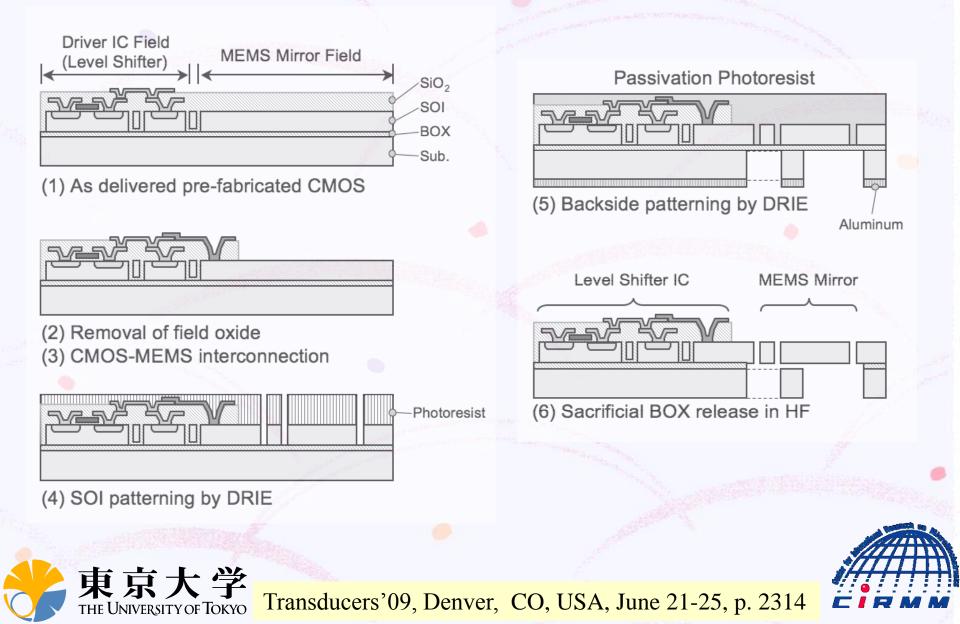

## **Post-CMOS MEMS** fabrication

Transducers'09, Denver, CO, USA, June 21-25, p. 2314 THE UNIVERSITY OF TOKYO

#### 2011.10.5

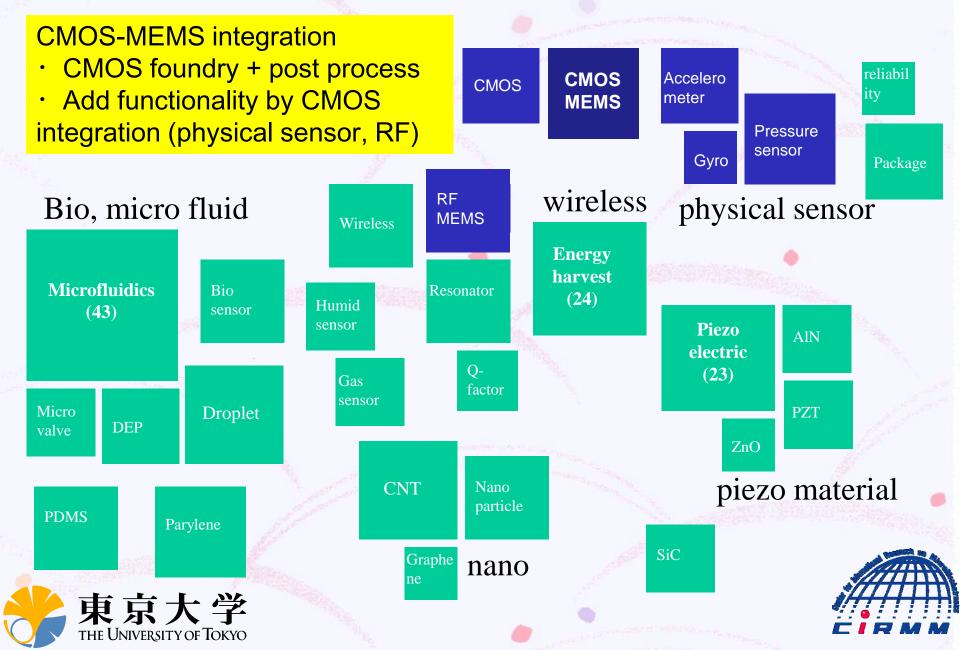

## Keyword statistics at Transducers 2011

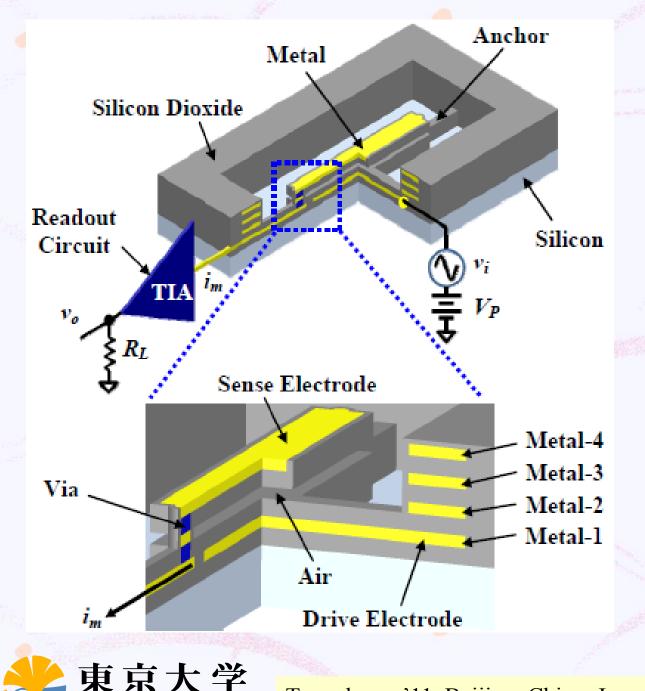

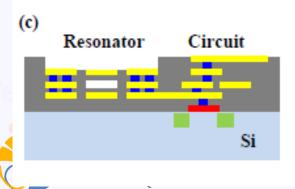

#### High-q, Large-Stopband-Rejection Integrated CMOS-MEMS Oxide Resonators with Embedded Metal Electrodes

Yu-Chia Liu<sup>1</sup>, Ming-Han Tsai<sup>1</sup>, Wen-Chien Chen<sup>2</sup>, Sheng-Shian Li1,<sup>2</sup> and Weileun Fang<sup>1,2</sup>

<sup>1</sup> Inst. of NanoEngineering and MicroSystems and <sup>2</sup> Dept. of Power Mechanical Engineering National Tsing Hua University, Hsinchu, Taiwan

THE UNIVERSITY OF TOKYO

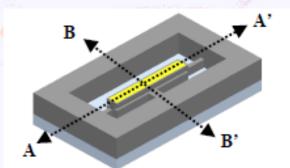

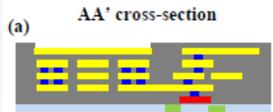

Perspective-view schematic of an electrode-embedded **CMOS-MEM oxide** resonator, including zoom-in of quarter cross-section view with signal transmission in a one-port test configuration.

2011.10.5

CMOS-MEMS chip in ceramic housing.

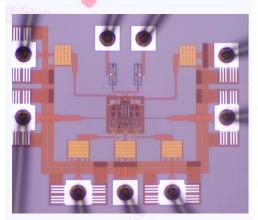

Die photo of monolithic *CMOS-MEMS integration.*

Table 1: Design Parameters of the Capacitively-Transduced CMOS-MEMS Oxide Resonator.

| Design Parameter                  | Value  | Unit    |

|-----------------------------------|--------|---------|

| Beam Length, $L_r$                | 55     | μm      |

| Beam Width, $W_r$                 | 4      | μm      |

| Air Gap, d <sub>o</sub>           | 0.64   | $\mu m$ |

| Oxide Thickness, h <sub>ox</sub>  | 1      | $\mu m$ |

| Structure Thickness, Hr           | 1.64   | $\mu m$ |

| Effective Mass, $m_r$             | 0.0388 | nkg     |

| Spring Constant, k <sub>r</sub>   | 102    | N/m     |

| Resonance Frequency (Calculation) | 2.58   | MHz     |

| Resonance Frequency (Simulation)  | 2.54   | MHz     |

Si

Drive Electrode

Si

#### **Fabrication sequence**

(a) a chip manufactured by standard TSMC 0.35 μm

2P4M process,

(b) metal wet etching to form resonator structure and transducer's gap, and

(c) RIE dry etch to open the electrode pads.

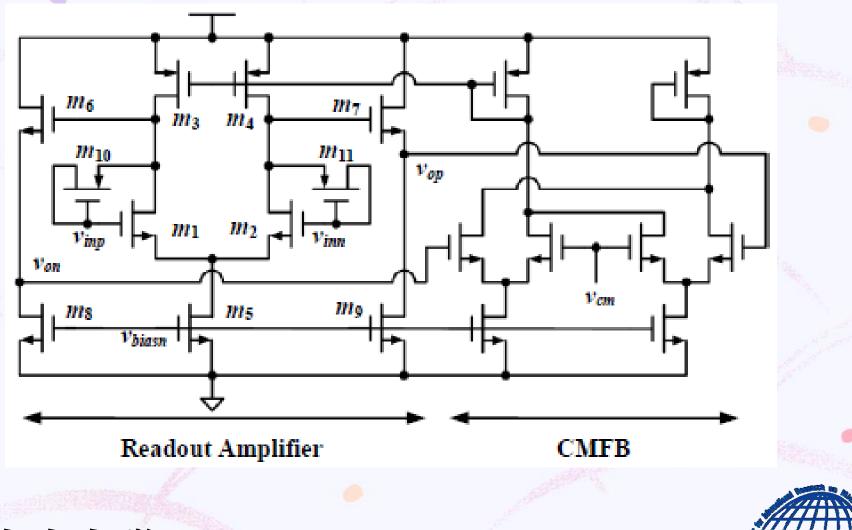

#### Schematic diagrams of a fully-differential readout amplifier.

京大学

THE UNIVERSITY OF TOKYO

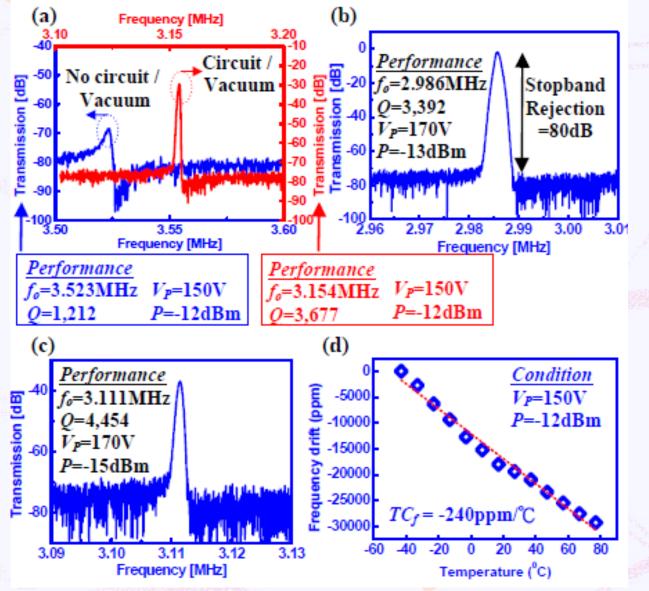

#### **Measurement results**

(a) with/without circuit tested in vacuum,

(b) frequency response with the highest stopband rejection,

(c) frequency response with the highest Q value,

(d) measured fractional frequency change versus temperature.

Table 2: CMOS-MEMS-Based Resonator Summary.

|                             | This work        | Ref [3]          | Ref [5]          | Ref [4]          |

|-----------------------------|------------------|------------------|------------------|------------------|

| Type                        | CC-Beam          | Beam             | SFR              | FF-Beam          |

| Materials                   | Metal +<br>Oxide | Metal +<br>Oxide | Metal +<br>Oxide | Metal +<br>Oxide |

| <i>f</i> <sub>o</sub> (MHz) | 3.11             | 6.33             | 6.18             | 14.5             |

| Q                           | ~3,300-4,400     | $\sim 100^{*}$   | ~1,000           | ~1,500           |

| <i>SB rej.</i><br>(dB)      | ~40-80           | ~4               | ~14              | ~10              |

<sup>\*</sup>Measured in atmospheric pressure.

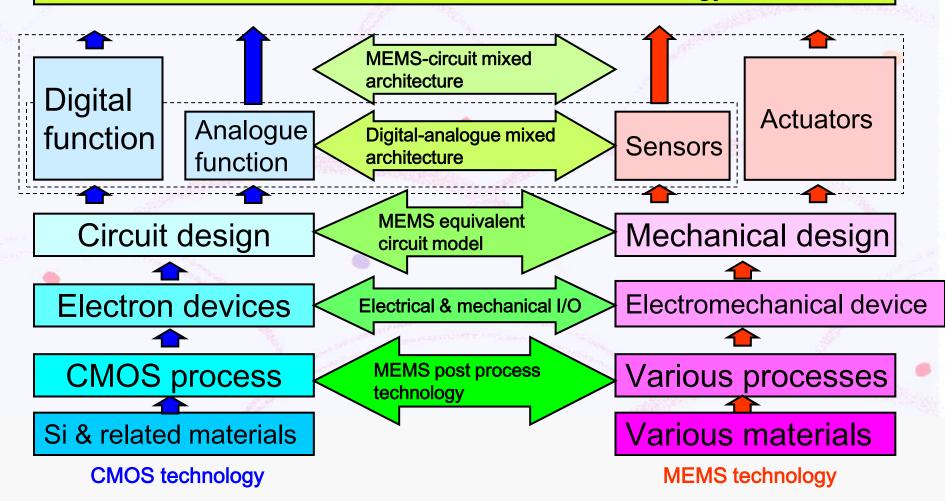

Hierarchical integration of design & fabrication steps for CMOS-MEMS technology

2011.10.5

Standardization of CMOS-MEMS technology

### MEMS equivalent circuit model generator

### http://memspedia.mmc.or.jp/WebLibrarySystem/

Useful to fill the gap between MEMS engineers and VLSI engineers

2011.10.5

# MEMS equivalent circuit model generator gyroscope comb-drive solid body beam

Connect basic components and construct a device beam + comb-drive + solid body = gyroscope

http://memspedia.mmc.or.jp/WebLibrarySystem/

### MEMS equivalent circuit model generator

#### Define connections

Simulated output

Each element is represented by an equivalent circuit. Connect them with external electrical circuit and perform SPICE simulation.

http://memspedia.mmc.or.jp/WebLibrarySystem/

-

2011.10.5

# Content

- MEMS trend toward MEMS-CMOS integration

- Examples of MEMS-CMOS integration

- Beyond MEMS-CMOS integration

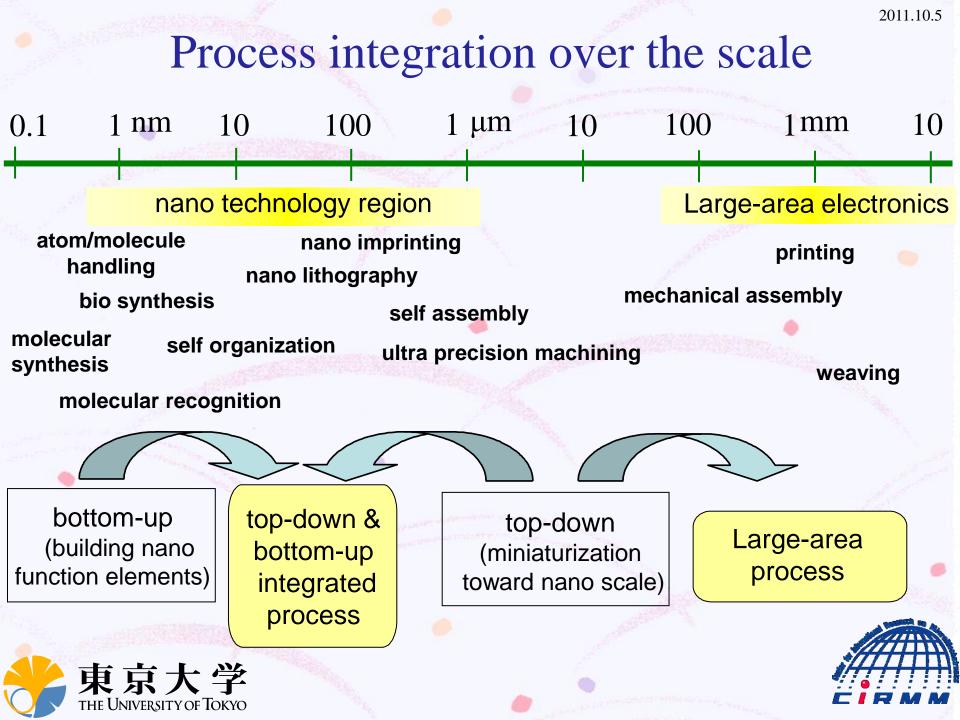

### Large-Area MEMS

THE UNIVERSITY OF TOKYO

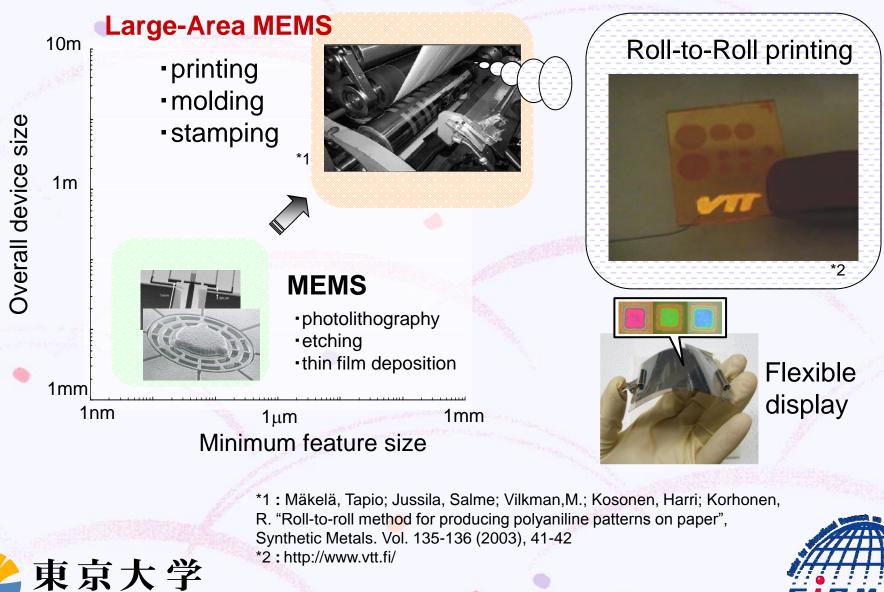

### Smart-skin wall paper and carpets

Room environment is kept comfortable by arrayed MEMS sensors and actuators.

Optical sensor + LED Microphone + speaker Temp. sensor + heater Humidity sensor + ventilator Human sensor on wall paper & carpet

Active MEMS carpet for cleaning

# Smart skin (intelligent surface) Taking best advantages of MEMS features 3M : Miniaturization , Multiple , Microelectronics

### Sensors + Local data processing + Actuators

APDIG

**Adaptative Wing**

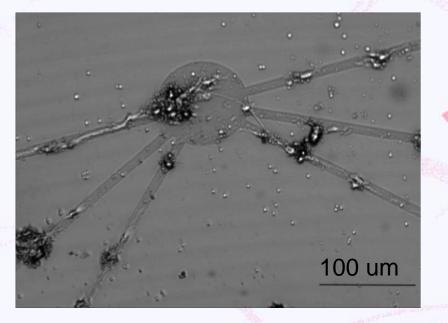

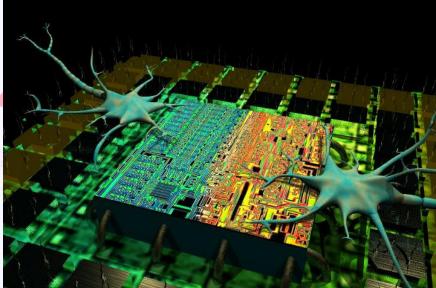

### MEMS guided axon for BMI 4-dimensional micromachining including temporal development

Cultured neuron cells elongate axons along micro patterns on a chip

**Prospected BMI**

### Future trends

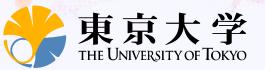

- Micro/nano machining technology in the future must be the integration of top-down methods (such as MEMS or VLSI) and bottom-up methods (such as molecular synthesis and bio technology).

- Autonomous MEMS instruments to capture ambient information will be important for security, personal health care, and environmental protection. Wireless devices and the MEMS energy source will play key role.

- New fabrication technology for large area integration of various functional devices will be important. Such products as flexible/interactive display, MEMS wall paper for lighting/air-conditioning/noise-reduction, and smart clothes may be produced.

### Conclusion

- MEMS Technology has matured and ready for CMOS-MEMS integration: *More-than-Moore*

- Four ways to integrate MEMS and CMOS. Hybrid integration is most practical. Fully mixed process and MEMS-first process are suitable to mass production of many devices. CMOS-first process is flexible and compatible with existing foundry system.

- Beyond CMOS-MEMS integration, bio/nano objects will be integrated on chip. Also process for smart skin will be required.

## Acknowledgment

- METI

- NEDO

- MMC/Beans laboratory

- COCN

- MEXT

- JSPS

- Global COE Program

- JST

- CNRS (France)

### In collaboration with

- Professors affiliated with CIRMM

- Hideki Kawakatsu, Hiroshi Toshiyoshi, Dominique Collard, Teruo Fujii, B. J. Kim, Shoji Takeuchi, Alan Bossebeouf, Takashi Kohno, A.-M. Tixier, Y. Rondelez, Masahiro Nomura

- Prof. Teruyasu Mizoguchi, Prof. Masao Washizu, Prof. T. Yatsui

- Students, post-Docs and visiting scientists

- Dr. Momoko Kumemura, Dr. M.C. Tarhan, Dr. C. Bottier, Mr. K.T. Qiu

- Dr. T. Ishida, Dr. L. Jalabert, Mr. T. Sato, Mr. S. Nabeya, Ms. Y. Takayama

- Japanese partners

- Prof. Yonezawa (Hokkaido Univ.) and his group

- Prof. Naruo Sasaki (Seikei Univ.) and his group

- Prof. Gen Hashiguchi (Shizuoka Univ.) and his group

- Prof. Ryuji Yokokawa (Kyoto Univ.) and his group

- Global partner

- Prof. Fabrizio Cleri (CNRS), Prof. Karl Boehringer (U. Washington), Prof. S. Karsten (UCLA)

- And many others...